Powering Biomedical Devices: Advanced AC-DC Conversion Circuits for Piezoelectric Energy Harvesting

This article provides a comprehensive technical guide on AC-DC conversion circuits tailored for piezoelectric transducers in biomedical applications.

Powering Biomedical Devices: Advanced AC-DC Conversion Circuits for Piezoelectric Energy Harvesting

Abstract

This article provides a comprehensive technical guide on AC-DC conversion circuits tailored for piezoelectric transducers in biomedical applications. Aimed at researchers and drug development professionals, it explores the foundational principles of piezoelectricity and rectification, details methodologies for full-wave and voltage-doubler circuits, offers troubleshooting for impedance mismatching and low-voltage startup, and presents validation metrics and comparisons of recent circuit architectures. The content synthesizes current research to enable the development of efficient, self-powered implantable sensors and biomedical systems.

From Vibration to Voltage: Core Principles of Piezoelectric Harvesting and Rectification

Application Notes: Energy Harvesting from Physiological Motion

Piezoelectric materials convert mechanical strain from physiological motions into alternating current (AC) electrical signals. This principle enables the development of self-powered medical devices and biosensors. The following table summarizes key performance metrics from recent studies.

Table 1: Quantitative Performance of Selected Piezoelectric Energy Harvesters for Physiological Motion

| Piezoelectric Material/Structure | Implantation Site / Motion Source | Open-Circuit Voltage (Vpp AC) | Output Power Density | Frequency of Motion (Hz) | Reference Year |

|---|---|---|---|---|---|

| PZT thin film on flexible substrate | Diaphragm (Respiratory) | 2.1 | 0.18 µW/cm² | 0.2 - 0.33 | 2023 |

| PVDF-TrFE nanofiber mat | Cardiac Apex (Heartbeat) | 4.8 | 1.2 µW/cm³ | 1.0 - 1.7 | 2024 |

| Biodegradable ZnO thin film | Peripheral Muscle (Limb Movement) | 0.85 | 8.6 nW/cm² | 0.5 - 3.0 | 2023 |

| Lead-free KNN-based composite | Jaw (Chewing) | 6.5 | 3.4 µW/cm² | 1.0 - 2.5 | 2024 |

| PZT ribbon with serpentine design | Lung Surface (Breathing) | 3.2 | 0.42 µW/cm² | 0.17 - 0.25 | 2023 |

Key Applications:

- Implantable Biosensors: Harvesting energy for continuous glucose monitors, neural activity sensors, and intracranial pressure monitors.

- Drug Delivery Systems: Powering miniaturized, programmable micropumps for chronotherapeutic drug release.

- Leadless Pacemakers: Supplementing battery life by converting cardiac motion into electrical energy.

- Wearable Health Monitors: Powering flexible patches that monitor vital signs (e.g., respiration rate, pulse).

Experimental Protocol: In-Vitro Characterization of a Piezoelectric Harvester for Muscle Motion

This protocol details the methodology for evaluating a flexible piezoelectric device intended for implantation on skeletal muscle.

AIM: To characterize the AC electrical output of a polyvinylidene fluoride-trifluoroethylene (PVDF-TrFE) based harvester under simulated physiological strain conditions.

MATERIALS:

- Fabricated PVDF-TrFE harvester (5 mm x 20 mm, encapsulated in biocompatible silicone).

- Electro-mechanical tester (e.g., Bose ElectroForce or similar with calibrated load cell).

- High-input impedance data acquisition system (DAQ, >10 MΩ) with differential probes.

- Oscilloscope.

- Custom mounting fixtures compatible with the tester and the harvester.

- Phosphate-buffered saline (PBS) solution, pH 7.4, at 37°C.

- Environmental chamber for the mechanical tester.

PROCEDURE:

- Mounting: Secure the ends of the piezoelectric harvester onto the fixtures of the electro-mechanical tester, ensuring the active bending zone is free. Connect the device's electrodes to the DAQ system.

- Environmental Conditioning: Place the mounted setup into the environmental chamber. Submerge the harvester in PBS solution at 37°C. Allow temperature to equilibrate for 30 minutes.

- Mechanical Stimulation Programming: Program the mechanical tester to apply cyclic tensile strain.

- Waveform: Sinusoidal.

- Strain Amplitude: Ramp from 0.1% to 1.5% in increments.

- Frequency Sweep: At each strain amplitude, perform a frequency sweep from 0.5 Hz to 5 Hz, covering the range of skeletal muscle motion.

- Cycles: 50 cycles per parameter set to ensure stable output.

- Data Acquisition: Simultaneously record the applied strain (from tester) and the generated AC voltage (from DAQ) for all test cycles. Use the oscilloscope to visually confirm waveform integrity.

- Load Characterization: At optimal strain/frequency (e.g., 1.0% strain, 2 Hz), connect a variable resistor load across the harvester terminals. Measure the RMS voltage across the load while varying resistance from 1 kΩ to 100 MΩ. Calculate output power (P = V²/R).

DATA ANALYSIS:

- Plot Open-Circuit Voltage (peak-to-peak) vs. Strain Amplitude and Frequency.

- Plot Output Power vs. Load Resistance to determine the optimal load and maximum power transfer.

- Calculate the effective piezoelectric coefficient (d₃₁ or d₃₃) from the slope of the charge-strain relationship.

The Scientist's Toolkit: Research Reagent Solutions

Table 2: Essential Materials for Piezoelectric Biomaterial Development & Testing

| Item / Reagent | Function / Purpose |

|---|---|

| Poly(vinylidene fluoride-co-trifluoroethylene) (PVDF-TrFE) | A flexible, biocompatible, and chemically inert piezoelectric polymer, often solution-processed into films or electrospun into fibers for soft, conformal harvesters. |

| Polydimethylsiloxane (PDMS), medical grade | A silicone elastomer used as a flexible, biocompatible encapsulation layer to protect the piezoelectric element from the biofluid environment and insulate electrical contacts. |

| Phosphate-Buffered Saline (PBS), pH 7.4 | A standard isotonic solution used for in-vitro testing to simulate the ionic composition and osmotic pressure of physiological fluids. |

| Piezoresponse Force Microscopy (PFM) Kit | A set of conductive cantilever tips and calibration standards used with an atomic force microscope (AFM) to locally map and quantify piezoelectric response at the nanoscale. |

| Biocompatible Epoxy (e.g., EP42HT-2Med) | Used for securing electrical connections and component assembly in implantable prototypes, offering long-term stability in wet environments. |

| Flexible Conductive Ink (e.g., Ag/AgCl flake in silicone) | Creates stretchable, low-impedance electrodes on flexible piezoelectric substrates that can withstand repeated deformation without cracking. |

| Impedance Analyzer (e.g., Keysight E4990A) | Characterizes the complex electrical impedance of the piezoelectric device across a frequency range, critical for designing matching AC-DC conversion circuits. |

Visualizations

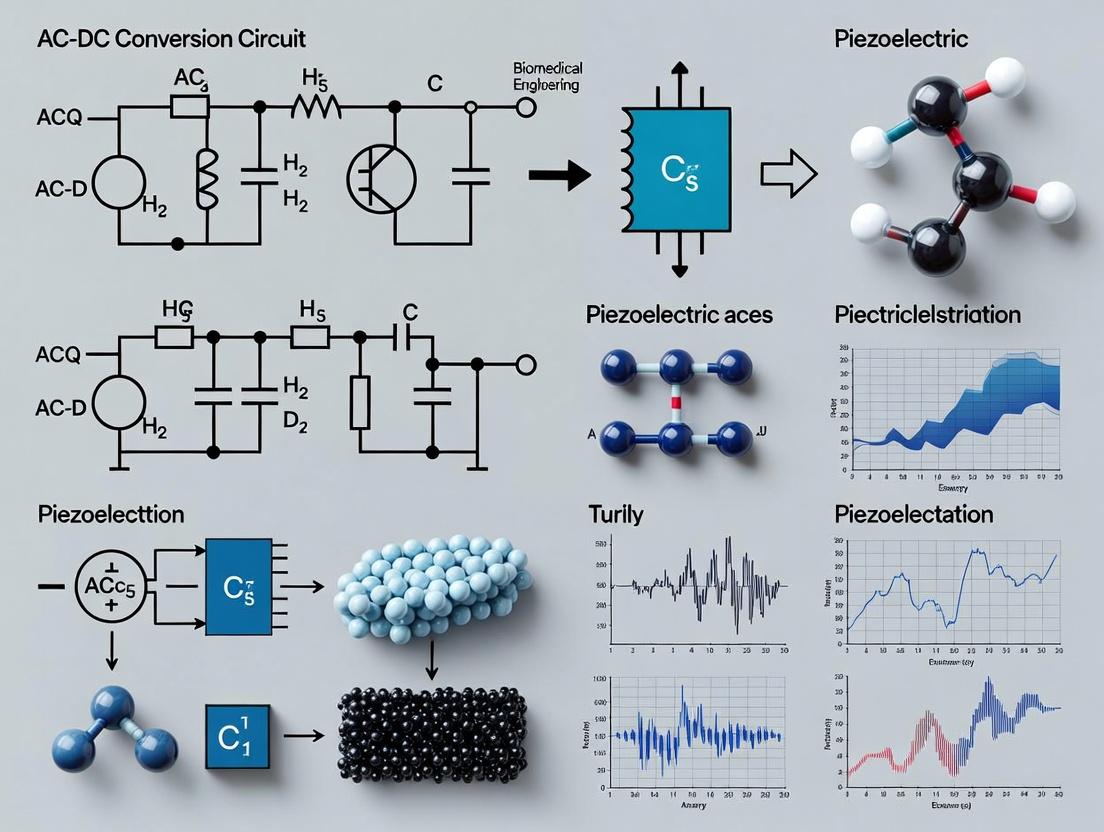

Diagram Title: Workflow from Body Motion to Powered Device

Diagram Title: Piezoelectric Biomedical Harvester Development Protocol

Application Notes: The Fundamental Necessity of Rectification

In the context of research on AC-DC conversion circuits for piezoelectric transducers, the rectification stage is an absolute prerequisite for practical energy harvesting and utilization. Piezoelectric materials generate alternating current (AC) in response to mechanical vibrations—a ubiquitous but irregular energy source in environments from industrial machinery to biomedical implants. To power consistent, usable direct current (DC) for sensors, microcontrollers, or drug delivery systems, this AC must be converted. Rectification, the process of converting bidirectional AC to unidirectional current, is the critical first step in this power conditioning chain. Without it, the harvested energy cannot be stored in capacitors or batteries, nor can it reliably power the vast majority of semiconductor-based electronic components and integrated circuits, which require stable DC bias voltages to operate. This conversion enables the transition from laboratory transduction principles to autonomous, self-powered devices for long-term monitoring and actuation.

Quantitative Comparison of Rectifier Topologies for Piezoelectric Harvesting

The choice of rectifier architecture significantly impacts the efficiency of energy extraction from a piezoelectric source. Key performance metrics include the input voltage threshold for activation and power conversion efficiency (PCE). The following table summarizes data from recent experimental studies on low-power (< 10 mW) piezoelectric energy harvesting.

Table 1: Performance Metrics of Common Rectifier Circuits for Piezoelectric Transducers

| Rectifier Topology | Typical Operating Voltage Range | Approximate Power Conversion Efficiency (PCE) | Key Advantage | Primary Limitation |

|---|---|---|---|---|

| Full-Wave Bridge (Passive) | > 0.7V (Diode Vf dependent) | 40-70% | Simplicity, robustness | High threshold voltage loss |

| Voltage Doubler (Cockcroft-Walton) | Very Low (< 0.3V) | 50-75% | Effective at low voltages | Requires more capacitors, load-dependent |

| Active Diode (Synchronous) | < 0.1V (MOSFET Rds(on) dependent) | 70-90% | Very low forward voltage drop | Requires control circuitry, complexity |

| Switching Boost Rectifier | Very Low (< 0.1V) | 65-85% | Integrated voltage step-up, high efficiency | Highest complexity, control overhead |

Experimental Protocol: Characterizing a Piezoelectric Energy Harvester with Full-Wave Bridge Rectification

Objective: To measure the DC output power and efficiency of a piezoelectric transducer (PZT) coupled with a passive full-wave bridge rectifier under controlled mechanical excitation.

Materials & Reagents:

- Piezoelectric cantilever (e.g., Mide Technology V21BL or equivalent).

- Electrodynamic shaker with power amplifier.

- Function generator.

- Full-wave bridge rectifier (composed of 4 Schottky diodes, e.g., BAT54S).

- Storage capacitor (e.g., 10 µF to 100 µF electrolytic).

- Programmable electronic load or precision resistor decade box.

- Oscilloscope with high-impedance probes.

- Laser displacement sensor (or calibrated accelerometer).

- Data acquisition system.

Procedure:

- Setup Calibration: Mount the PZT cantilever securely to the shaker armature. Use the laser displacement sensor to measure the tip displacement of the cantilever. Drive the shaker via the function generator and power amplifier at the PZT's resonant frequency (determined via a prior frequency sweep). Calibrate the input acceleration (g-level) to the shaker's driving voltage.

- Circuit Assembly: Solder the full-wave bridge rectifier using the Schottky diodes. Connect the output of the PZT to the AC input terminals of the bridge. Connect the positive and negative DC output terminals of the bridge to the storage capacitor in parallel with the programmable electronic load.

- Open-Circuit Voltage Measurement: Set the electronic load to a high-resistance state (>1 MΩ). Subject the PZT to a fixed mechanical excitation (e.g., 0.5g at resonance). Use the oscilloscope to measure the peak-to-peak open-circuit AC voltage (VAC(p-p)) directly from the PZT terminals. Then, measure the steady-state DC voltage (VDC(oc)) across the storage capacitor.

- Power Delivery Measurement: Set the electronic load to a specific resistive value (RL). Allow the system to reach steady-state. Record the DC voltage (VDC) across the load. Calculate the delivered DC power: PDC = VDC2 / RL.

- Efficiency Calculation: For the same excitation condition, measure the AC voltage (VAC(rms)) and current (IAC(rms)) at the input to the rectifier using oscilloscope math functions. Calculate the available AC input power: PAC = VAC(rms) * IAC(rms). The rectifier stage efficiency is: ηrect = (PDC / PAC) * 100%.

- Sweep Parameters: Repeat steps 4-5 for a range of load resistances (e.g., 1 kΩ to 1 MΩ) and/or input acceleration levels. Plot PDC vs. RL to identify the optimal load for maximum power transfer.

The Scientist's Toolkit: Research Reagent Solutions for Piezoelectric Energy Harvester Testing

Table 2: Essential Materials for Piezoelectric AC-DC Conversion Research

| Item | Function/Explanation |

|---|---|

| Lead Zirconate Titanate (PZT) Cantilevers | Standard piezoelectric element providing high electromechanical coupling; the AC voltage source for the experiment. |

| Low-Dropout Schottky Diodes (e.g., BAT54 series) | Core rectification component; minimizes the forward voltage loss (~0.3V) compared to standard silicon diodes (~0.7V), crucial for low-voltage PZT outputs. |

| Polymer-based Solid-State Capacitors | Energy storage buffer; low equivalent series resistance (ESR) is critical for efficiently capturing short, high-frequency current pulses from the rectifier. |

| Wideband Electrodynamic Shaker System | Provides precise, controllable, and repeatable mechanical excitation to the PZT at specified frequencies and amplitudes. |

| Precision Programmable DC Electronic Load | Enables systematic sweeps of load resistance to find the maximum power point (MPP) of the complete harvesting circuit without manual resistor swapping. |

Visualization: Piezoelectric Harvesting System Workflow

Diagram Title: Piezoelectric Energy Harvesting Signal Chain

Visualization: Rectifier Topology Decision Logic

Diagram Title: Rectifier Selection Logic Flow

This application note details the core electrical characteristics of piezoelectric transducers (PZTs) essential for their integration into AC-DC conversion circuits. As part of a broader thesis on energy harvesting for biomedical applications—such as powering implantable drug delivery systems—understanding these parameters is fundamental. Efficient AC-DC conversion maximizes harvested power from mechanical vibrations, directly impacting the viability of self-powered medical devices.

Core Electrical Characteristics

Fundamental Parameters & Data

Piezoelectric transducers are governed by a constitutive equation coupling mechanical and electrical domains. For power harvesting, the simplified equivalent circuit is a sinusoidal current source, (ip(t) = Ip \sin(\omega t)), in parallel with an internal capacitance ((Cp)) and resistance ((Rp)). Key measurables are derived from this model.

Table 1: Key Electrical Characteristics of Representative Piezoelectric Transducers

| Transducer Type/Material | Typical Open-Circuit Voltage (Voc), peak | Typical Short-Circuit Current (Isc), peak | Internal Capacitance, Cp (nF) | Optimal Resistive Load (kΩ) | Max Power Output (µW) |

|---|---|---|---|---|---|

| PZT-5A (Ceramic, 1 cm²) | 10 - 50 V | 10 - 50 µA | 20 - 100 | 50 - 500 | 100 - 1000 |

| PVDF (Polymer Film) | 5 - 20 V | 1 - 10 µA | 0.5 - 5 | 500 - 5000 | 5 - 50 |

| MFC (Macro Fiber Composite) | 30 - 100 V | 5 - 20 µA | 5 - 30 | 200 - 1000 | 200 - 500 |

| ZnO Nanowire Array | 0.1 - 2 V | 0.01 - 0.5 µA | 0.01 - 0.1 | 1000 - 10000 | 0.001 - 0.1 |

Note: Values are highly dependent on excitation frequency, amplitude, transducer geometry, and mounting. Data compiled from recent literature (2021-2024).

Characteristic Definitions

- Open-Circuit Voltage (Voc): The peak voltage measured across the transducer terminals when no load is connected. It represents the maximum potential difference the transducer can generate under specific mechanical excitation.

- Short-Circuit Current (Isc): The peak current measured when the transducer terminals are connected with negligible impedance. It represents the maximum charge displacement current.

- Optimal Load (Zopt): The load impedance (often purely resistive for initial analysis) at which the electrical power delivered to the load is maximized. For a resistive load ((RL)), (Z{opt} \approx 1/(\omega Cp)) at the excitation frequency (\omega), neglecting (Rp).

Experimental Protocols

Protocol 1: Measurement of Voc, Isc, and Cp

Objective: To characterize the basic electrical output parameters of a PZT. Materials: See Scientist's Toolkit. Method:

- Mounting: Securely mount the PZT to a calibrated shaker or vibration source using a recommended adhesive (e.g., cyanoacrylate).

- Excitation: Apply a known, fixed sinusoidal mechanical excitation (e.g., 1g RMS at 100 Hz). Record frequency ((f)) and acceleration ((a)).

- Voc Measurement: Connect a high-impedance oscilloscope or differential voltage probe (>10 MΩ) directly across the PZT leads. Measure the peak sinusoidal voltage. (V{oc} = V{measured, peak}).

- Isc Measurement: Replace the oscilloscope with a low-resistance current sense resistor (e.g., 10-100 Ω) or a current probe. Measure the peak voltage across the sense resistor and calculate (I{sc} = V{sense, peak} / R_{sense}).

- Cp Measurement: Disconnect the PZT from the shaker. Using an LCR meter, measure the capacitance between the PZT leads at a low frequency (e.g., 1 kHz). This is the internal capacitance (C_p).

Protocol 2: Determination of Optimal Resistive Load and Maximum Power

Objective: To experimentally find the load resistance that maximizes power output. Method:

- Set up the PZT under the same fixed mechanical excitation as in Protocol 1.

- Connect a variable decade resistor box or a set of precision resistors across the PZT terminals.

- For each load resistor value ((RL)), use an oscilloscope to simultaneously measure the peak voltage ((V{L,peak})) across the load and the peak current ((I_{L,peak})) through it.

- Calculate RMS power for each load: (P{L, RMS} = (V{L,peak} / \sqrt{2}) \times (I{L,peak} / \sqrt{2}) = (V{L,peak} \times I_{L,peak}) / 2).

- Plot (P{L, RMS}) versus (RL). The resistance at the peak of the curve is the optimal resistive load ((R_{opt})).

- The corresponding power is the maximum harvestable power for a simple resistive load.

Diagrams for Characterization & Circuit Integration

Title: PZT Characterization & Optimal Load Determination Workflow

Title: From Piezoelectric Effect to Key Electrical Parameters

The Scientist's Toolkit: Research Reagent Solutions & Essential Materials

Table 2: Essential Materials for PZT Electrical Characterization

| Item / Reagent | Function / Explanation |

|---|---|

| Piezoelectric Transducer | Device Under Test (DUT). Common types: PZT ceramics (high output), PVDF films (flexible), MFCs (robust). |

| Electrodynamic Shaker | Provides controlled, reproducible mechanical vibration excitation at known frequencies and amplitudes. |

| Function Generator & Amp | Drives the shaker with a clean sinusoidal signal. Allows precise control of excitation frequency. |

| Low-Noise Charge Amplifier | Alternative to voltage measurement; directly converts piezoelectric charge to voltage, minimizing cable effects. |

| High-Impedance Oscilloscope | Measures high-voltage signals without loading the PZT circuit (input impedance ≥10 MΩ). |

| Precision LCR Meter | Measures the internal capacitance (Cp) and dielectric loss of the PZT at rest. |

| Variable Decade Resistor Box | A set of high-precision, switchable resistors used to sweep load resistance (RL) during optimization. |

| Calibration Accelerometer | Mounted near the PZT to accurately measure the applied mechanical acceleration input. |

| Low-Capacitance Coaxial Cable | Minimizes signal attenuation and parasitic capacitance during high-impedance voltage measurements. |

| Anisotropic Conductive Adhesive | For mounting PZTs without shorting electrodes; maintains mechanical coupling. |

Within research into AC-DC conversion circuits for piezoelectric energy harvesting transducers, the standard diode bridge rectifier remains a fundamental interface component. Piezoelectric transducers generate low-voltage, alternating current (AC) output under mechanical excitation, necessitating efficient rectification for powering microelectronic devices or sensors. This application note details the operation, inherent efficiency limits, and critical threshold voltage challenges of the diode bridge rectifier in this specific research context, providing protocols for empirical characterization.

Operation Principle

A standard full-wave bridge rectifier employs four diodes arranged in a bridge configuration. It converts bidirectional AC input from a piezoelectric transducer into unidirectional pulsating DC output.

- Positive Half-Cycle: Current flows through one diode pair to the load.

- Negative Half-Cycle: Current flows through the other diode pair, maintaining the same polarity across the load.

The output is subsequently smoothed by a filter capacitor (C_f).

Quantitative Analysis of Efficiency Limits and Voltage Challenges

The primary efficiency limitation stems from the forward voltage drop (V_f) across each diode. For a standard silicon p-n junction diode, V_f is approximately 0.7V. During each half-cycle, the input AC voltage must overcome two series diode drops (2V_f ≈ 1.4V). For low-voltage piezoelectric outputs (often < 5V peak), this represents a significant loss, reducing the available output voltage and conversion efficiency.

Table 1: Impact of Diode Threshold on Rectifier Performance for Piezoelectric Inputs

| Piezoelectric Open-Circuit Voltage (V_peak) | Ideal DC Output (V) | Practical DC Output (considering 2*V_f loss) | Estimated Power Loss Percentage |

|---|---|---|---|

| 1.5 V | 1.5 V | ~0.1 V (severely clipped) | > 90% |

| 3.0 V | 3.0 V | ~1.6 V | ~ 44% |

| 5.0 V | 5.0 V | ~3.6 V | ~ 28% |

| 10.0 V | 10.0 V | ~8.6 V | ~ 14% |

Table 2: Comparison of Diode Technologies for Low-Voltage Rectification

| Diode Type | Typical Forward Voltage (V_f) | Advantage | Disadvantage |

|---|---|---|---|

| Standard Silicon (1N4007) | 0.65 - 1.00 V | Low cost, robust | High loss for low-voltage inputs |

| Schottky (e.g., 1N5817) | 0.15 - 0.45 V | Lower V_f, faster switching | Higher reverse leakage current, moderate cost |

| Germanium | ~0.3 V | Low turn-on voltage | Temperature sensitivity, less common |

| Active (Synchronous) | ~0.05 V (Rdson dependent) | Very low effective voltage drop, high efficiency | Complex drive circuitry, higher cost, parasitics |

Experimental Protocols

Protocol 4.1: Characterizing Rectifier Efficiency with Piezoelectric Input

Objective: To measure the voltage and power efficiency of a standard diode bridge under simulated piezoelectric excitation. Materials: Function generator, standard diode bridge (1N400x or equivalent), Schottky diode bridge (1N581x or equivalent), load resistors (10 kΩ to 1 MΩ), oscilloscope, digital multimeters (2), filter capacitor (e.g., 10 µF), solderless breadboard. Procedure:

- Set the function generator to produce a sinusoidal waveform with frequency 50-200 Hz (typical for many piezoelectric transducers) and variable amplitude (1-10 V_peak).

- Construct the standard diode bridge rectifier circuit with a filter capacitor and a load resistor (e.g., 100 kΩ) on the breadboard.

- Connect the function generator output to the AC input terminals of the bridge.

- Using Oscilloscope Channel 1, measure and record the peak input voltage (V_in_peak). Using Channel 2, measure the DC output voltage (V_out_dc) across the load.

- Use DMMs to precisely measure the RMS input voltage and DC output voltage. Calculate input power (P_in = V_in_rms² / R_source_est) and output power (P_out = V_out_dc² / R_load). Note: The source impedance must be estimated or measured separately.

- Calculate voltage efficiency: η_V = (V_out_dc / V_in_peak) * 100%.

- Calculate power efficiency: η_P = (P_out / P_in) * 100%.

- Repeat steps 4-7 for varying input voltages and load resistances.

- Replace the standard diode bridge with a Schottky diode bridge and repeat the entire experiment.

- Tabulate results for comparative analysis.

Protocol 4.2: Threshold Voltage Drop Measurement

Objective: To directly measure the forward voltage drop of the rectifier bridge as a function of current. Materials: DC power supply, current-limiting resistor (1 kΩ), diode bridge, ammeter, voltmeter. Procedure:

- Connect the DC power supply in series with the current-limiting resistor, the ammeter, and the DC output terminals of the bridge (treating it as a two-terminal device). Leave AC input terminals open.

- Connect the voltmeter directly across the DC output terminals.

- Slowly increase the supply voltage from 0V. The bridge will conduct when the voltage exceeds 2V_f.

- Record the voltage (V_bridge) and current (I) at multiple points as current increases (e.g., 0.1mA, 1mA, 10mA).

- Plot V_bridge vs. I. The y-intercept approximates the total threshold voltage (2V_f) of the bridge.

Diagrams and Visualizations

Title: Piezoelectric Energy Harvesting with Standard Diode Bridge

Title: Rectifier Selection Decision Flow

The Scientist's Toolkit: Research Reagent Solutions

Table 3: Essential Materials for Piezoelectric Rectifier Research

| Item / Reagent Solution | Function / Explanation in Research Context |

|---|---|

| Low-Frequency Function Generator | Simulates the AC output waveform of a piezoelectric transducer for controlled, repeatable bench testing. |

| Standard Silicon Diode Bridge (e.g., 1N4007) | Baseline rectifier component for establishing performance benchmarks and illustrating threshold limitations. |

| Schottky Diode Bridge (e.g., SB1100, 1N5819) | Low-V_f alternative for improving efficiency with moderate-voltage piezoelectric sources. |

| High-Input-Impedance Oscilloscope | Essential for accurate measurement of low-current, high-impedance piezoelectric and rectifier node voltages. |

| Precision Digital Multimeter (DMM) | Measures true RMS AC input and DC output voltages/currents for power and efficiency calculations. |

| Variable Resistive Load Bank | Emulates the varying power consumption of target microelectronic loads (sensors, wireless transmitters). |

| Filter Capacitor Kit (1nF to 1000µF) | For investigating output ripple versus efficiency trade-offs during the smoothing stage. |

| Prototype Active Rectifier IC (e.g., LTC3588, MAX17710) | Integrated solution combining ultra-low-V_f synchronous rectification with power management for direct comparison. |

| Piezoelectric Cantilever Test Bench | Provides standardized mechanical excitation (shaker or impact) to characterize rectifiers with actual transducers. |

This review synthesizes recent advances (2022-2024) in low-power energy harvesting (EH) for implantable biomedical devices, framed within a broader thesis research on optimizing AC-DC conversion circuits for piezoelectric transducers (PZTs). The primary challenge is efficiently converting the irregular, low-amplitude AC output from miniature PZTs into stable, usable DC power for implants. Trends indicate a shift towards holistic system co-design, encompassing the transducer, power management integrated circuit (PMIC), and storage, with a focus on sub-1 cm³ form factors and µW-to-mW power budgets.

Table 1: Performance Metrics of Recent Implantable Energy Harvesting Systems (2022-2024)

| Harvesting Source | Peak Output Power (Reported) | Volume / Form Factor | Key AC-DC Topology | Application Target | Ref. Year |

|---|---|---|---|---|---|

| Piezoelectric (PZT, Body Motion) | 15 - 40 µW/cm³ | < 1 cm³ | Active Rectifier + Fractional Open-Circuit Voltage (FOCV) MPPT | Cardiac & Neuromodulation | 2023 |

| Triboelectric Nanogenerator (TENG) | ~200 µW (peak) | Flexible, thin film | Synchronous Electric Charge Extraction (SECE) | Wearable/Implantable Biosensors | 2022 |

| Biofuel Cell (Glucose) | 3 - 50 µW/cm² | Miniaturized chip | Boost Converter with Cold Start | Continuous Glucose Monitors | 2024 |

| RF Harvesting (ISM Band) | 1 - 100 µW (range-dependent) | Miniaturized antenna array | Multi-stage Dickson Charge Pump | Deep Implant Telemetry | 2023 |

| Photovoltaic (Subdermal) | 10 - 25 µW/mm² (under skin) | Array of micro-cells | Hybrid Buck/Boost Converter | Optogenetic Stimulation | 2023 |

Table 2: Comparison of AC-DC Converter Architectures for PZT Harvesting

| Converter Topology | Typical Efficiency (%) | Startup Voltage | Control Complexity | Suitability for Irregular PZT Output |

|---|---|---|---|---|

| Full-Bridge Passive Rectifier | 60-75 | Zero (theoretical) | Low | Poor (Diode drop loss) |

| Active Diode (Synchronous) Rectifier | 75-90 | Requires bias (~200mV) | Medium | Good |

| Voltage Doubler / Dickson Charge Pump | 65-80 | Low | Medium | Moderate |

| SECE (Synchronous Electric Charge Extraction) | 80-92 | High | High | Excellent |

| FOCV-based Buck/Boost | 70-85 | Medium | High | Good with MPPT |

Detailed Experimental Protocols

Protocol 1: Characterizing PZT Output for Implant-Mimicking Conditions

- Objective: To measure the open-circuit voltage (Voc) and short-circuit current (Isc) of a microscale PZT under simulated physiological mechanical excitations.

- Materials: See Scientist's Toolkit (Table 3).

- Method:

- Mount the miniature PZT (e.g., 5x5x1 mm³) on a programmable shaker, embedded in a PDMS slab to mimic tissue encapsulation.

- Apply sinusoidal mechanical excitation with frequency sweeps (1-100 Hz) and displacement amplitudes (0.01-0.1 mm) simulating cardiac or respiratory motion.

- Connect the PZT electrodes directly to a high-impedance oscilloscope (for Voc) and a low-impedance picoammeter (for Isc).

- Record time-domain waveforms. Calculate peak power density (µW/cm³) as (Voc * Isc)/4 at matched impedance, averaged over 100 cycles.

- Export data for modeling the Thevenin equivalent circuit of the PZT source.

Protocol 2: Evaluating Active Rectifier with FOCV MPPT for PZT

- Objective: To test the end-to-end efficiency of a custom AC-DC conversion circuit.

- Materials: See Scientist's Toolkit (Table 3).

- Method:

- Fabricate/procure the PMIC featuring an active rectifier (using near-zero-Vth MOSFETs) and an FOCV-based buck converter. Set the sampling fraction (k) to 0.7 initially.

- Use the setup from Protocol 1. Connect the PZT output to the PMIC input.

- Connect a programmable electronic load (modeling an implant, e.g., 10-100 kΩ) at the DC output.

- Apply a specific mechanical excitation (e.g., 20 Hz, 0.05 mm). Measure:

- Input Power (Pin): Calculate from the rectifier's input voltage/current waveform.

- Output Power (Pout): Measure DC voltage across the load.

- Calculate total system efficiency: η = (Pout / Pin) * 100%.

- Vary the excitation parameters and load to map the system's performance envelope.

Visualizations

(PZT Harvesting & Power Management Flow)

(PZT Harvesting System Development Workflow)

The Scientist's Toolkit: Research Reagent Solutions

Table 3: Essential Materials for PZT Harvesting Circuit Research

| Item / Reagent | Function / Rationale | Example Product / Specification |

|---|---|---|

| Micro-scale PZT Element | The core transducer; converts mechanical stress to AC voltage. | Piezo.com, PIC255 (5x5x1 mm³), high d₃₃ coefficient. |

| Programmable Linear Shaker | Provides precise, repeatable mechanical excitation for in-vitro testing. | TIRA/Vibration Test Systems, Model LDS V455. |

| PDMS (Polydimethylsiloxane) | Silicone elastomer used to encapsulate PZT, simulating tissue damping. | Dow Sylgard 184 Kit. |

| Low-Threshold Voltage MOSFETs | Critical for active rectifier design to minimize forward voltage drop (~100mV). | TSMC 65nm CMOS or discrete devices (e.g., Vishay SiS442DN). |

| Supercapacitor / Thin-Film Battery | Temporary energy storage buffer for pulsed implant operation. | CAP-XX HS230 (Supercap) or Cymbet CBC-EVAL-12 (Solid-State Battery). |

| Ultra-Low Power PMIC Eval Board | Platform for prototyping AC-DC conversion and MPPT algorithms. | Texas Instruments BQ25570EVM or Analog Devices LTC3588-1. |

| High-Impedance Oscilloscope | Measures high V_oc of PZT without loading the source. | Keysight InfiniiVision, 1 MΩ / 10 pF input. |

| Semiconductor Parameter Analyzer | Characterizes I_sc and full I-V curves of the harvesting source. | Keysight B1500A. |

Circuit Design and Implementation: Architectures for Efficient Biomedical Energy Harvesting

In the broader research on AC-DC conversion circuits for piezoelectric transducers, the full-wave bridge rectifier is a critical interface stage. Piezoelectric transducers, used in applications from energy harvesting to biomedical drug delivery systems, generate alternating current (AC) under mechanical excitation. Efficient and reliable rectification is essential to convert this low-amplitude, variable-frequency AC into usable direct current (DC) for powering microelectronic circuits, sensors, or controlled drug release mechanisms. This application note details the standard topology, component selection rationale, and layout protocols optimized for this research context, where output stability, efficiency, and minimal voltage drop are paramount.

Standard Topology and Operational Principle

The standard single-phase, full-wave diode bridge rectifier consists of four diodes arranged in a closed-loop bridge configuration. The AC input is connected across the two opposite nodes of the bridge, while the DC output is taken from the other two nodes, with a smoothing capacitor placed across the DC output terminals.

During the positive half-cycle of the AC input, two diodes become forward-biased, creating a current path to the load. During the negative half-cycle, the other two diodes conduct. This process results in both halves of the input waveform being utilized, producing a pulsating DC output with double the frequency of the input AC. The smoothing capacitor reduces the ripple voltage.

Component Selection for Piezoelectric Transducer Applications

Selection is driven by the characteristic high output impedance, low current (µA to mA), and potentially variable voltage/ frequency of piezoelectric transducers.

Table 1: Quantitative Data for Component Selection

| Component | Key Parameter | Typical Range for Piezo Applications | Selection Rationale |

|---|---|---|---|

| Diode | Forward Voltage (Vf) | 0.2V - 0.3V (Schottky) | Minimizes conduction losses; critical for low-voltage piezo outputs. |

| Reverse Leakage Current | < 1 µA | Prevents significant discharge of the storage capacitor. | |

| Reverse Recovery Time | Fast / Ultra-fast (< 50 ns) | Essential for high-frequency vibration harvesting. | |

| Smoothing Capacitor | Capacitance Value | 10 µF - 1000 µF (Electrolytic/Tantalum) | Determines ripple voltage; larger values for higher current/lower ripple. |

| Equivalent Series Resistance (ESR) | Low ESR types preferred | Reduces power loss and internal heating. | |

| Rated Voltage | 2-3x max expected Vdc | Ensures reliability and safety margin. | |

| Load / Reservoir Capacitor | Capacitance, Type | 1 mF - 10 mF (Supercapacitor) | Stores harvested energy for burst operation of downstream circuits. |

| Piezo Transducer Model | Open-Circuit Voltage (Voc), Short-Circuit Current (Isc) | Voc: 1-50 Vpk, Isc: 1µA-10mA | Source impedance (Voc/Isc) dictates optimal rectifier input impedance. |

Experimental Protocols for Rectifier Characterization

Protocol 4.1: Efficiency Measurement under Simulated Piezo Source Objective: To measure the power conversion efficiency (η) of the bridge rectifier when driven by a simulated piezoelectric transducer source.

- Setup: Use a function generator in series with a high-value resistor (Rs) to simulate the piezo's open-circuit voltage (Voc) and internal impedance. Rs = Voc (simulated) / Isc (desired).

- Circuit Connection: Connect this simulated source to the input of the bridge rectifier under test. Connect the specified smoothing capacitor (Csmooth) and electronic load (Rload) to the DC output.

- Measurement: Use a digital oscilloscope with two voltage probes and one current probe (or a series sense resistor).

- Probe 1: Measure AC input voltage (V_ac).

- Probe 2 & Current Probe: Measure DC output voltage (Vdc) and current (Idc).

- Data Acquisition: Record Vac(rms), Vdc(avg), Idc(avg). Calculate input power as Pin = Vac(rms)² / Rs (approximation for high Rs). Calculate output power as Pout = Vdc(avg) * Idc(avg).

- Calculation: η = (Pout / Pin) * 100%. Repeat for varying Rs, frequency, and V_ac to map performance.

Protocol 4.2: Ripple Voltage Quantification Objective: To determine the peak-to-peak ripple voltage (V_ripple) at the rectifier output.

- Setup: Use the finalized rectifier circuit with a constant resistive load.

- Measurement: Connect an oscilloscope probe directly across the smoothing capacitor terminals. Set coupling to AC to remove the DC offset.

- Analysis: Measure the peak-to-peak voltage of the observed waveform. This is Vripple. Correlate with load current and capacitor value (Csmooth). Vripple ≈ Iload / (f * C_smooth), where f is the ripple frequency (2 * input AC frequency).

Protocol 4.3: Start-Up Voltage Threshold Test Objective: Critical for energy harvesting; determines the minimum piezo voltage required to begin conduction.

- Setup: Use a low-voltage, slowly ramping function generator (e.g., 0-5V at 0.1Hz) in series with Rs as the source.

- Observation: Monitor DC output voltage with a high-impedance voltmeter.

- Determination: The input voltage at which V_dc first becomes measurable (e.g., > 20mV) is the start-up threshold, typically ~2*Vf of the diodes.

Layout Considerations for Research Prototypes

- Minimize AC Loop Area: Keep the AC input traces between the piezo and the bridge tight and short to reduce radiated noise and inductive losses.

- Star Ground for DC: Route all DC return paths (capacitor grounds, load ground) to a single point near the bridge ground to avoid circulating currents.

- Thermal Management: For higher current (>10mA) prototypes, provide small copper pours for the diodes to dissipate heat.

- Parasitic Minimization: Place the smoothing capacitor physically close to the bridge output terminals to minimize series inductance which increases ripple.

- Test Point Inclusion: Include labeled solder pads or vias for critical nodes (AC in+, AC in-, V_dc, GND) for easy oscilloscope probing.

The Scientist's Toolkit: Research Reagent Solutions

Table 2: Essential Materials for Rectifier Prototyping & Testing

| Item | Function / Explanation |

|---|---|

| Schottky Diode Kit (e.g., BAT54 series, 1N5817-9) | Low Vf diodes for testing optimal efficiency. Different voltage/current ratings allow for design optimization. |

| Low-ESR Electrolytic/Tantalum Capacitor Kit | For smoothing capacitor selection. Tantalum offers lower leakage but higher cost. |

| Surface-Mount Prototyping Boards | Allows for compact, low-parasitic layout as described in Section 5. |

| Piezoelectric Transducer Simulator | A benchtop instrument or custom circuit (function gen + power resistor) to reliably replicate piezo source characteristics for controlled experiments. |

| High-Impedance Active Oscilloscope Probe | Essential for accurately measuring high-impedance nodes (e.g., piezo output, rectifier input) without loading the circuit. |

| Programmable Electronic Load | Enables precise sweeping of load current (I_dc) to characterize rectifier performance under varying conditions. |

| Thermal Imaging Camera (or IR Sensor) | For identifying unexpected heating in diodes or capacitors, indicating excessive losses or incorrect component choice. |

Diagrams

Title: Piezo to DC Power Conversion Pathway

Title: Rectifier Design & Validation Workflow

This application note is situated within a broader thesis research program focused on Advanced AC-DC Conversion Circuits for Low-Power Piezoelectric Transducers. The primary challenge addressed is the inherently low and alternating current (AC) output voltage from piezoelectric elements used in applications such as self-powered biomedical sensors and energy harvesters for portable diagnostic devices. Voltage doubler circuits, specifically the Greinacher (single-stage) and multi-stage Cockcroft-Walton (CW) multiplier topologies, provide a critical function by rectifying and stepping up these low AC voltages to usable DC levels for powering downstream electronics, data loggers, or drug delivery system actuators.

Key Circuit Architectures: Comparative Analysis

The following table summarizes the core quantitative characteristics of the two primary circuit families.

Table 1: Comparison of Greinacher & Cockcroft-Walton Voltage Doubler Circuits

| Parameter | Greinacher (1-Stage) Voltage Doubler | N-Stage Cockcroft-Walton Multiplier | Notes / Implications |

|---|---|---|---|

| No. of Diodes | 2 | 2N | N = number of stages. Higher component count. |

| No. of Capacitors | 2 | N+1 | |

| Theoretical DC Output (No Load) | 2 * Vpeak | (2N) * Vpeak | Vpeak is peak AC input voltage. |

| Practical Output (Under Load) | ~2 * Vpeak - (Iload / (f * C)) | ~(2N * Vpeak) - (Iload / f * C) * (2/3 N³ + N²/2 - N/6) | f = input frequency, C = stage capacitance. CW exhibits significant voltage drop and ripple under load. |

| Optimal Input Frequency Range | 10 Hz - 10 kHz | >100 Hz (typically kHz range) | Piezo outputs often <1kHz. CW performance degrades at low frequency. |

| Output Ripple | Lower | Higher (increases with N and Iload) | Critical for sensitive electronic loads. |

| Key Advantage | Simplicity, better low-frequency/low-current performance. | High voltage gain from a low input. | Enables usable voltage from very weak piezo sources. |

| Primary Disadvantage | Limited multiplication factor. | Poor voltage regulation and efficiency under load. | |

| Typical Piezo Application | Boosting output for micro-sensors, low-power logic. | Energy harvesting from ambient vibration for battery charging. |

Experimental Protocol: Characterizing a 4-Stage CW Multiplier for a Piezoelectric Harvester

Objective: To measure the DC output voltage and power transfer efficiency of a 4-stage CW multiplier connected to a simulated piezoelectric transducer under varying mechanical excitation frequencies.

Protocol 3.1: Circuit Fabrication & Test Setup

Materials & Reagents:

- Function Generator: Simulates piezoelectric AC voltage output.

- High-Input-Impedance Oscilloscope: Measures AC input and DC output waveforms.

- Low-Leakage, High-Frequency Diodes (e.g., 1N4148 or Schottky BAT54): For minimal forward voltage drop.

- Low-ESR, High-Frequency Ceramic Capacitors (100nF - 1µF): Stage capacitors.

- Precision Load Resistors (10kΩ - 1MΩ): To simulate electronic load.

- Breadboard or PCB and Interconnects.

- Digital Multimeter: For DC voltage/current validation.

Procedure: a. Construct the 4-stage CW ladder network as per the standard topology. b. Connect the AC input terminals to the function generator output. c. Connect the DC output terminals (

Vout+andVout-) across a parallel combination of a load resistor (start with 1MΩ) and an oscilloscope probe (DC coupled). d. Connect a second oscilloscope probe (AC coupled) across the function generator terminals to monitor input. e. Set the function generator to produce a sinusoidal waveform with an amplitude of 3.0 Vpeak (simulating a strong piezo signal) and a frequency of 500 Hz. f. Power on the instruments and record the no-load DC output voltage. g. Systematically decrease the load resistance (increase load) from 1MΩ to 10kΩ in logarithmic steps. At each step, allow the circuit to stabilize, then record the DC output voltage and calculate the output power (P = V²/R).

Protocol 3.2: Data Collection & Efficiency Calculation

- For each load condition (RL), record:

- Vinpeak (from oscilloscope)

- Voutdc (from oscilloscope or DMM)

- f (fixed at 500 Hz).

- Calculate for each point:

- Output Power (Pout): Pout = (Voutdc)² / RL

- Input Power Approximation (Pin): For an ideal sinusoid into a resistive load, Pin = (Vinrms)² / Rin. However, the multiplier presents a non-linear load. A practical approximation is to measure the current drawn from the source using a current probe or a small series sense resistor and calculate Pin = Vinrms * Iinrms.

- Conversion Efficiency (η): η = (Pout / Pin) * 100%.

- Tabulate results as shown below.

Table 2: Sample Data from 4-Stage CW Multiplier Characterization (Vin_peak=3V, f=500Hz, C=220nF)

| Load RL (kΩ) | Measured Vout_dc (V) | Theoretical Vout (V) | Output Power Pout (µW) | Estimated Efficiency η (%) |

|---|---|---|---|---|

| 1000 (No Load) | 21.8 | 24.0 | 0.48 | N/A |

| 100 | 18.5 | 24.0 | 3.42 | ~25% |

| 47 | 15.1 | 24.0 | 4.85 | ~18% |

| 22 | 10.8 | 24.0 | 5.30 | ~12% |

| 10 | 6.2 | 24.0 | 3.84 | ~6% |

Visualizing the System Workflow and Core Circuit

Title: Piezo Energy Harvesting & Conversion Workflow

Title: Greinacher & 2-Stage CW Circuit Diagrams

The Scientist's Toolkit: Essential Research Reagents & Materials

Table 3: Key Research Reagent Solutions for Piezo-Voltage Multiplier Experiments

| Item / Reagent | Specification / Example | Primary Function in Research |

|---|---|---|

| Piezoelectric Element | PZT-5A, PVDF film, or MEMS piezo cantilever. | The transducer under test; converts mechanical energy to AC electrical energy. |

| Low Vf Diodes | Schottky (BAT54S, 1N5817) or Ultra-Fast Silicon (1N4148). | Core rectifying element; lower forward voltage (Vf) minimizes losses. |

| Low-ESR Capacitors | Ceramic (C0G/NP0 dielectric), 10nF - 10µF. | Stage capacitors for charge storage/pumping; low Equivalent Series Resistance (ESR) improves efficiency. |

| Programmable Load | Electronic load module or high-precision resistor decade box. | Simulates the power consumption of downstream circuits to test regulation and efficiency. |

| Vibration Exciter | Shaker table or calibrated piezoelectric actuator. | Provides controlled, reproducible mechanical excitation to the piezo element. |

| Signal Conditioning Buffer | High-input-impedance, low-noise op-amp circuit (e.g., LTC6268). | Interposes between high-impedance piezo and multiplier to prevent signal loading. |

| Energy Storage Element | Low-leakage supercapacitor (e.g., 0.1F, 5.5V) or thin-film battery. | Stores the rectified DC output for burst power delivery to loads. |

Application Notes

Within the research context of AC-DC conversion circuits for piezoelectric transducers, optimizing rectification efficiency is paramount. Piezoelectric harvesters generate low-voltage, high-impedance AC outputs, making traditional diode rectifiers (with ~0.3-0.7V forward voltage, Vf) extremely lossy. Active diode and synchronous rectification (SR) circuits replace diodes with actively controlled MOSFETs, reducing the effective voltage drop to the MOSFET's on-resistance (RDS(on)) losses, often in the millivolt range. This directly increases the harvested power and usable voltage for downstream electronics, such as sensors or drug delivery system controllers in biomedical research.

1. Core Principles & Quantitative Comparison The following table summarizes key performance metrics for standard and active rectification topologies relevant to piezoelectric energy harvesting (PEH).

Table 1: Rectifier Topology Performance Comparison for Low-Voltage PEH

| Parameter | Standard Full-Bridge (Diode) | Active Diode (Gate-Driven) | Full Synchronous Rectifier |

|---|---|---|---|

| Typical Voltage Drop | 2 * Vf (~0.6V - 1.4V) | I*RDS(on) (e.g., 20-100mV) | I*RDS(on) (e.g., 20-100mV) |

| Control Complexity | None (Passive) | Moderate (Comparator/LTspice) | High (Dedicated IC or MCU) |

| Quiescent Power Draw | 0 µA | 5 - 50 µA | 10 - 200 µA |

| Ideal Input Voltage Range | > 2V (for efficiency) | 0.5V - 10V | 0.3V - 10V |

| Key Loss Components | Conduction (Vf), Reverse Recovery | Conduction (RDS(on)), Control | Conduction (RDS(on)), Switching, Control |

| Typical Efficiency Gain | Baseline | 15-40% increase | 20-60% increase |

2. Research Reagent Solutions & Essential Materials Table 2: Essential Components for Synchronous Rectifier Prototyping in PEH Research

| Item / Component | Example Part(s) | Function / Rationale |

|---|---|---|

| Low-Threshold N-MOSFET | DMP2035U, IRLB8721 | Core switching element. Very low gate threshold voltage (Vgs(th) < 1.5V) enables activation from low PEH voltages. |

| Low-Power Comparator | LTC1540, TS881 | Provides digital control signal for MOSFET gates by comparing drain-source voltage. Ultra-low supply current is critical. |

| Synchronous Rectifier IC | LTC3588-1, TPS22810 | Integrated solution for PEH. Contains full SR bridge, regulator, and storage management, simplifying system design. |

| Piezoelectric Transducer | Mide V21BL, PI Ceramic PIC255 | The AC energy source. Characterized by its open-circuit voltage (Voc) and short-circuit current (Isc) parameters. |

| Load/Storage Emulator | Electronic Load, Capacitor Bank | Simulates the downstream research load (e.g., sensor, battery) for controlled efficiency measurements. |

| Low-Leakage Input Capacitor | C0G/NP0 Ceramic, 100nF | Provides a local AC coupling point, minimizes charge loss before rectification. |

| Gate Drive Buffer (Optional) | TC7WU04FU (Inverter as buffer) | Strengthens comparator output to switch MOSFETs faster, reducing cross-conduction in full-bridge SR. |

3. Experimental Protocols

Protocol 3.1: Characterization of Baseline Diode Rectifier Losses Objective: Establish the efficiency baseline for a given piezoelectric transducer.

- Setup: Connect the PEH to a standard full-wave diode bridge (using 1N5817 Schottky diodes). Connect the rectifier output to a variable resistive load through a current shunt. Place voltage probes across the PEH output and the load.

- Mechanical Excitation: Use a calibrated shaker table to subject the PEH to a defined sinusoidal mechanical excitation (e.g., 0.5g RMS at 120 Hz). Maintain consistency across all experiments.

- Data Acquisition: Sweep the load resistance from open-circuit to short-circuit conditions. For each point, record:

- AC input voltage (Vacpeak) from the PEH.

- DC output voltage (Vdc) across the load.

- DC output current (Idc) via shunt voltage.

- Analysis: Calculate input AC power (approximated as Vacrms * Iacrms, requiring current probe) and output DC power (Vdc * Idc). Plot efficiency (η = Pdc / Pac) vs. load resistance.

Protocol 3.2: Implementation and Tuning of a Single-Active-Diode Rectifier Objective: Replace one diode in the bridge with an active MOSFET to quantify improvement.

- Circuit Assembly: Construct the circuit per the logical workflow diagram (Fig. 1). Use a low-Vgs(th) NMOS (e.g., DMP2035U). The comparator (LTC1540) senses the voltage between MOSFET source and drain.

- Control Voltage Calibration: Power the comparator from a stable, low-voltage supply (e.g., 3.3V). Without excitation, verify that the comparator output is low (MOSFET off). Briefly short the rectifier output to observe the comparator output going high.

- Dynamic Testing: Repeat the mechanical excitation from Protocol 3.1. Record Vdc and Idc across the same load sweep.

- Optimization: Adjust the hysteresis (if added via feedback resistors) on the comparator to minimize shoot-through current and oscillation. Measure the quiescent current of the control circuit.

Protocol 3.3: Full-Bridge Synchronous Rectification Using Dedicated IC Objective: Achieve maximum efficiency using an integrated synchronous rectifier solution.

- System Configuration: Interface the PEH directly with the input of an IC like the LTC3588-1. Configure the IC's rectifier for "active" or "synchronous" mode via its configuration pins. Connect a storage capacitor (e.g., 100µF) and a representative load (e.g., a 100kΩ resistor in parallel with a wireless sensor module).

- Efficiency Measurement: This protocol measures end-to-end conversion efficiency from mechanical input to regulated DC output.

- Measure the mechanical input power to the shaker (if accessible) or use a calibrated reference transducer to infer transmitted vibration power.

- At the LTC3588-1 output, measure the regulated DC voltage and current supplied to the load.

- Comparison: Compare the total harvested energy over a set time period against the baseline from Protocol 3.1.

4. Mandatory Visualizations

Within the broader thesis research on AC-DC conversion circuits for piezoelectric energy harvesting, optimizing power extraction from ambient mechanical vibrations remains a critical challenge. Standard interface circuits, such as the full-bridge rectifier, suffer from limited bandwidth and suboptimal power transfer due to the inherent electrical impedance mismatch with the piezoelectric transducer. This application note details advanced techniques—Synchronized Switch Harvesting on Inductor (SSHI) and Synchronized Electric Charge Extraction (SECE)—that address these limitations. These nonlinear interfacing methods are pivotal for applications requiring robust, self-powered systems, such as wireless sensor networks for remote monitoring in pharmaceutical development and scientific research facilities.

Core Principles and Comparative Analysis

SSHI and SECE circuits enhance power extraction by synchronously manipulating the piezoelectric voltage to improve energy extraction per cycle. The table below summarizes their key operational characteristics and quantitative performance gains compared to a standard rectifier.

Table 1: Comparison of Piezoelectric Interface Circuit Techniques

| Parameter | Standard Rectifier | SSHI (Parallel) | SECE |

|---|---|---|---|

| Core Principle | Passive rectification of piezoelectric open-circuit voltage. | Synchronized inversion of piezo voltage via a switched LC network to reduce voltage cancellation. | Extraction of all stored charge on piezo capacitor at its displacement extremum via a switched-mode converter. |

| Typical Power Gain | 1x (Baseline) | 4x - 10x | 3x - 6x |

| Bandwidth | Narrow (High Q-factor) | Significantly Broadened (Up to 4x) | Very Broad (Virtually constant power vs. frequency) |

| Circuit Complexity | Low (Diodes, capacitor) | Medium (Switch, inductor, control logic) | High (Switch, inductor, transformer/DC-DC, control logic) |

| Control Requirement | None | Requires peak detection of displacement/voltage. | Requires peak detection and precise switching for charge extraction. |

| Optimal Load | Resistive, matched to piezo impedance. | Resistive, but less sensitive to load variation. | Can be designed for a wide range of load resistances. |

| Key Limitation | Low efficiency, narrow bandwidth. | Performance degrades with poor synchronization. | Higher component count and switching losses. |

Experimental Protocols for Circuit Characterization

Protocol 3.1: Baseline Power-Frequency Characterization of a Piezoelectric Transducer

Objective: To establish the inherent bandwidth and maximum power output of a piezoelectric transducer with a standard full-bridge rectifier interface. Materials: See Section 5: The Scientist's Toolkit. Procedure:

- Mount the piezoelectric transducer (PZT) on a calibrated electromagnetic shaker.

- Connect the PZT electrodes to a full-bridge rectifier followed by a storage capacitor (Cstorage) and a variable resistive load (Rload).

- Set the shaker to a base acceleration (e.g., 0.5g RMS) using a signal generator and power amplifier. Verify with an accelerometer.

- Sweep the excitation frequency across the expected resonant range (e.g., ±5 Hz from the estimated resonance) in small increments (e.g., 0.1 Hz).

- At each frequency point, allow the system to reach steady-state, then measure the DC voltage (Vdc) across Rload using a high-impedance voltmeter.

- Calculate extracted power: ( P = V{dc}^2 / R{load} ).

- Plot Power vs. Frequency to determine the half-power bandwidth and peak power.

Protocol 3.2: Evaluation of SSHI Circuit Performance

Objective: To quantify the bandwidth broadening and power gain achieved by a parallel SSHI circuit. Materials: See Section 5. Procedure:

- Replace the standard rectifier in Protocol 3.1 with a parallel SSHI interface circuit. The circuit consists of a switch (typically a MOSFET) in series with an inductor (L_sshi), placed in parallel with the PZT after the rectifier bridge.

- Implement a synchronous switch control circuit. This circuit monitors the PZT voltage (or the rectified DC voltage) and triggers the switch closure for a short duration (determined by ( \pi\sqrt{L{sshi}C{pzt}} )) when the displacement/voltage reaches a maximum/minimum.

- Repeat the frequency sweep from Protocol 3.1, steps 4-6.

- Compare the resulting Power vs. Frequency plot with the baseline. Measure the increase in peak power and the widening of the half-power bandwidth.

Protocol 3.3: Evaluation of SECE Circuit Performance

Objective: To measure the load-independent and broadband power extraction capability of a SECE interface. Materials: See Section 5. Procedure:

- Interface the PZT with a SECE circuit. A typical topology involves a switch in series with the primary winding of a transformer (or a DC-DC converter), connected directly across the PZT electrodes (no front-end rectifier).

- Implement control logic that closes the switch at the instant of maximum displacement (and thus maximum voltage, Vp), transferring the stored energy ( \frac{1}{2}C{pzt}V_p^2 ) to the transformer's magnetic field. The energy is then delivered to the load on the secondary side.

- Set the shaker to a fixed frequency at the PZT's mechanical resonance. Measure the output power across a range of load resistances (e.g., 1 kΩ to 1 MΩ).

- Repeat the power measurement at several off-resonance frequencies.

- Compare the power versus load and power versus frequency data against the baseline and SSHI results, noting the relative insensitivity to both parameters.

System Architecture and Signal Flow Visualizations

The Scientist's Toolkit: Research Reagent Solutions

Table 2: Essential Materials and Equipment for Piezoelectric Interface Research

| Item | Specification / Example | Function in Experiment |

|---|---|---|

| Piezoelectric Transducer | Mide Technology V21BL, PIC255 ceramic | The energy harvesting element; converts mechanical strain to electrical charge. Key parameters: d31/g31 coefficient, capacitance (C_pzt), resonant frequency. |

| Electromagnetic Shaker | Brüel & Kjær Type 4810 or similar | Provides precise, controllable mechanical vibration input to the PZT for frequency sweeps. |

| Signal Generator & Power Amplifier | Keysight 33500B, Trek PZD700 | Drives the shaker with a tunable frequency and amplitude signal. |

| High-Impedance Active Probe | Tektronix TAP1500 (1.5 GHz) | Minimizes loading effects when measuring high-voltage, high-impedance PZT signals. |

| Precision Digital Multimeter | Keithley DMM6500 | Measures DC output voltage and current accurately for power calculations. |

| Low-Loss Inductor | Air-core or ferrite-core, value tuned to PZT capacitance (e.g., 10-100 mH) | Forms the resonant LC network with C_pzt for voltage inversion in SSHI circuits. |

| Fast Power MOSFET | Infineon IRFZ44N, Vishay SiRxxx | The core switching element in SSHI and SECE circuits. Low R_ds(on) and gate charge are critical. |

| Gate Driver IC | Texas Instruments UCC27324 | Provides the necessary current to rapidly switch the MOSFET ON/OFF, minimizing switching losses. |

| Microcontroller / FPGA | STM32F4, Xilinx Spartan-6 | Implements the peak/zero detection algorithms and generates precise, synchronized switching signals. |

| Low-Leakage Storage Capacitor | Film capacitor (e.g., Polypropylene), 1-10 µF | Temporarily stores harvested energy before delivery to the load. Low ESR and leakage are vital. |

Application Notes

Context within Piezoelectric AC-DC Conversion Research

For piezoelectric energy harvesting (PEH) systems, the raw AC output from the transducer is highly irregular, low-voltage, and impedance-mismatched with typical electronic loads. A PMU is the critical intermediary that performs AC-DC conversion, impedance matching, voltage regulation, and energy storage management. This integration is paramount for powering low-power sensors and devices in remote or biomedical settings, including applications relevant to drug development research, such as implantable physiological monitors or wireless sensor networks for laboratory environments.

Core Functional Blocks of a PEH-PMU System

- AC-DC Rectification: A full-bridge or voltage doubler rectifier converts the bipolar piezoelectric output to a DC voltage. Advanced techniques like synchronous rectification using active switches minimize voltage drop and improve efficiency.

- Impedance Matching & Maximum Power Point Tracking (MPPT): To maximize harvested power, the PMU's input stage must present an optimal load resistance to the piezoelectric element. Simple, low-power MPPT algorithms (e.g., Fractional Open-Circuit Voltage) are often implemented.

- DC-DC Regulation & Conversion: A DC-DC converter (e.g., buck, boost, or buck-boost) steps the rectified voltage to a level suitable for the storage element and the load. It provides a stable, regulated output.

- Energy Storage Management: This block controls the charging profile for storage elements (supercapacitors or thin-film batteries) to prevent overcharging and manage depth-of-discharge, critically impacting cycle life.

- Load Management & Power Gating: The PMU intelligently powers the load (e.g., a microcontroller, sensor, and RF transmitter) in duty-cycled bursts, ensuring energy consumption remains below the harvesting rate.

Storage Element Selection: Supercapacitors vs. Batteries

Table 1: Quantitative Comparison of Storage Technologies for Piezoelectric PMUs

| Parameter | Supercapacitor (Electric Double-Layer) | Thin-Film/Lithium-Polymer Battery |

|---|---|---|

| Energy Density (Wh/kg) | 1 - 10 | 100 - 250 |

| Power Density (W/kg) | 1,000 - 10,000 | 500 - 2,000 |

| Cycle Life | >500,000 cycles | 300 - 1,000 cycles |

| Charge Time | Seconds to minutes | Minutes to hours |

| Efficiency | 85% - 98% (charging) | 70% - 85% (charging) |

| Self-Discharge Rate | High (10-40%/month) | Low (1-5%/month) |

| Voltage Profile | Linear with State-of-Charge (SoC) | Relatively flat during discharge |

| Typical Application in PEH | Burst-power loads, frequent cycling | Sustained, lower-power operation |

Recommendation: For intermittent, high-peak-power loads (e.g., transmitting a data packet), a supercapacitor is preferred. For maintaining a steady, low-level background operation (e.g., continuous sensing), a battery is superior. A hybrid solution is often optimal.

Experimental Protocols

Protocol A: Characterizing PMU Efficiency with a Piezoelectric Transducer

Objective: To measure the end-to-end power conversion efficiency of a PMU prototype under simulated piezoelectric input conditions.

Materials & Equipment:

- Function Generator (e.g., Keysight 33500B)

- Power Amplifier (e.g., TA0533 from Newtons4th Ltd)

- Reference Piezoelectric Transducer (or a calibrated capacitor + resistor network)

- PMU Prototype Board

- Programmable Electronic Load (e.g., BK Precision 8500)

- Digital Storage Oscilloscope (e.g., Tektronix MDO3000)

- Precision Current Probes / Differential Voltage Probes

Procedure:

- Setup: Connect the power amplifier output to the piezoelectric transducer terminals. Connect the PMU input to the transducer. Connect the regulated PMU output to the electronic load.

- Simulate Harvesting: Configure the function generator to produce a sinusoidal waveform at the transducer's resonant frequency (e.g., 50-200 Hz). Set the amplitude on the power amplifier to achieve the desired open-circuit AC voltage (e.g., 3-10 Vpp).

- Input Measurement: Use the oscilloscope with current and differential voltage probes to measure the instantaneous voltage (Vin(t)) and current (Iin(t)) at the PMU input. Calculate average input power (P_in) over one complete cycle.

- Output Measurement: Measure the regulated DC output voltage (Vout) and current (Iout) using the oscilloscope or the electronic load's readback. Calculate output power (Pout = Vout * I_out).

- Efficiency Sweep: For a fixed input frequency and amplitude, vary the electronic load resistance across a wide range (e.g., 1 kΩ to 1 MΩ). Record Pin and Pout at each point.

- Calculation: Compute total efficiency η = (Pout / Pin) * 100% for each load point. Identify the optimal load for maximum power transfer.

Protocol B: Evaluating Storage Charging & Load Management

Objective: To profile the charging characteristics of a supercapacitor from a piezoelectric-PMU system and test active load switching.

Materials & Equipment:

- Full PEH-PMU system from Protocol A.

- Supercapacitor (e.g., 0.1F, 5.5V).

- Programmable Microcontroller Unit (MCU) as dynamic load (e.g., ARM Cortex-M0+).

- Digital Multimeter for long-term logging.

- Environmental Chamber (optional, for temperature variation).

Procedure:

- Initialization: Fully discharge the supercapacitor. Set the PMU's storage output to charge the supercapacitor. Ensure the load MCU is disconnected.

- Charging Profile: Apply a continuous mechanical excitation (via shaker) or electrical simulation to the transducer. Record the supercapacitor voltage (V_sc) over time using the multimeter until it reaches the PMU's charge termination voltage.

- Load Burst Testing: Once Vsc reaches a predefined threshold (e.g., 3.0V), program the PMU's load switch to power the MCU load for a fixed duration (e.g., 2 seconds) to perform a simulated task (sensor read & data transmit). Monitor the dip in Vsc.

- Duty Cycling: After the load burst, the PMU isolates the load and resumes charging the supercapacitor. Program this charge-burst-dormancy cycle to repeat. Measure the average load power and compare it to the average harvested power to assess system sustainability.

Diagrams

Diagram 1: PMU Functional Blocks in Piezoelectric System

Diagram 2: Experiment Flow for PMU Efficiency

The Scientist's Toolkit

Table 2: Key Research Reagent Solutions & Materials

| Item | Function / Description |

|---|---|

| Piezoelectric Cantilever (MFC Type) | Macro-Fiber Composite transducer; provides robust, flexible mechanical coupling and high voltage output for bench-top energy harvesting experiments. |

| Electrodynamic Shaker (e.g., Brüel & Kjær) | Provides precise, controllable mechanical excitation to the piezoelectric element, simulating real-world vibration sources at defined frequencies and amplitudes. |

| Low-Power PMU Evaluation Kit (e.g., LTC3588, BQ25570) | Integrated circuit platform for rapid prototyping. Contains essential blocks: rectifier, MPPT, DC-DC converter, and storage charger. |

| Low-ESR Supercapacitor (e.g., Maxwell, Panasonic) | High-cyclability storage element for testing burst-energy delivery and rapid charge/discharge cycles characteristic of PEH systems. |

| Precision Differential Voltage Probe (e.g., Tektronix THDP0100) | Enables accurate, floating measurement of small AC voltages at the piezoelectric terminals without grounding issues. |

| Ultra-Low-Power Microcontroller (e.g., Texas Instruments MSP430) | Serves as the programmable, dynamic load for load management experiments. Can be duty-cycled to simulate real sensor node behavior. |

| Source Measure Unit (SMU) (e.g., Keithley 2450) | Can act as a programmable load and precision voltage/current source/sinker for characterizing storage elements and PMU sub-circuits. |

This application note is framed within a broader thesis research on optimizing AC-DC conversion circuits for low-frequency, irregular piezoelectric energy harvesters. The focus is on extracting usable electrical power from physiological motions (cardiac and respiratory) to perpetually operate a wireless biosensor node, eliminating the need for battery replacement in implantable or wearable drug delivery monitors.

The following table summarizes quantitative data from recent key studies on harvesting energy from cardiac and respiratory motion.

Table 1: Performance Summary of Recent Physiological Motion Energy Harvesters

| Ref. (Year) | Harvester Type | Target Motion | Peak Output Voltage (V) | Peak Output Power (µW) | Optimal Frequency (Hz) | AC-DC Topology Used | Sensor Node Function Demonstrated |

|---|---|---|---|---|---|---|---|

| Zheng et al. (2024) | Flexible Piezo-Composite Patch | Cardiac (Epicardial) | 4.2 (AC) | 3.5 | 1.2 (Swine) | Active Full-Bridge Rectifier + LTC3588 | Bluetooth Low Energy (BLE) Heart Rate Telemeter |

| Occhiuzzi et al. (2023) | PZT Cantilever with Inertial Mass | Respiratory (Chest Wall) | 8.1 (AC) | 15.0 | 0.25 (Human) | Voltage Doubler + BQ25570 | Capacitive Humidity & Temperature Sensor (RFID backscatter) |

| Wang et al. (2023) | Kirigami-Structured PVDF Film | Respiratory (Diaphragmatic) | 6.8 (AC) | 11.2 | 0.3 (Rat) | Synchronized Switch Harvesting on Inductor (SSHI) | Glucose Level Monitor & Drug Release Trigger |

| Lee & Kiani (2022) | Implantable Piezo-Stack | Cardiac (Ventricular) | 7.5 (AC) | 8.7 | 1.5 (Porcine) | Full-Wave Rectifier + MAX17710 | Endocardial Pressure Sensing & Data Logging |

Experimental Protocols

Protocol 3.1: In-Vitro Characterization of Piezoelectric Patches for Respiratory Motion

Objective: To determine the electrical output and optimal load of a flexible piezoelectric harvester under simulated respiratory strain and frequency.

Materials:

- Linear Motor Stage (e.g., Thorlabs LTS300)

- Function Generator

- Flexible PZT Composite Patch (e.g., Mide Technology Volture)

- Precision Variable Resistor Box (1 kΩ to 10 MΩ)

- Oscilloscope (High-Impedance Input)

- Precision Digital Multimeter

- Simulated Lung/Thorax Mechanical Fixture

Procedure:

- Fixture Mounting: Securely clamp the edges of the piezoelectric patch to the linear motor's moving platform and a fixed base, imposing a bending strain.

- Motion Profile: Program the linear motor to replicate human tidal breathing: A sinusoidal displacement of 5-10 mm at a frequency of 0.2 Hz (12 breaths/minute) and 0.33 Hz (20 breaths/minute).

- Open-Circuit Voltage: With the harvester disconnected from any load, measure the peak-to-peak AC voltage (V_oc) output directly using the oscilloscope.

- Power Sweep: Connect the harvester outputs to the variable resistor box in series with the multimeter (current measurement). Sweep the load resistance from 1 kΩ to 10 MΩ logarithmically.

- Data Recording: For each resistance value (RL), record the RMS voltage (VL) across the load. Calculate output power using Pout = (VL)^2 / R_L.

- Optimal Point: Identify the load resistance (Ropt) that yields the maximum power (Pmax). Plot Pout vs. RL.

Protocol 3.2: In-Vivo Validation in a Porcine Model for Cardiac Energy Harvesting

Objective: To measure the harvested energy from an epicardially implanted device during normal sinus rhythm and under varying hemodynamic conditions.

Materials:

- Porcine model (40-50 kg)

- Sterile, Biocompatible Piezo-Harvester (e.g., encapsulated PZT thin film)

- Clinical-grade Physiological Monitor

- Implantable Data Logger with High-Efficiency AC-DC Circuit (e.g., based on BQ25504)

- Supercapacitor (e.g., 10 mF, 5V)

- Surgical Suite for Sterile Procedure

Procedure:

- Pre-Implant Benchmark: Prior to surgery, characterize the harvester's output under calibrated bending cycles matching expected cardiac deformation.

- Surgical Implantation: Under general anesthesia and following IACUC-approved protocols, perform a left lateral thoracotomy. Suture the sterile harvester patch onto the anterolateral aspect of the left ventricle.

- Circuit Connection: Connect the harvester leads to the input of the implanted AC-DC power management unit (PMU), which is connected to the supercapacitor and data logger.

- Data Acquisition: Close the chest and allow the animal to recover. Record over 24 hours:

- PMU input voltage/current (from harvester).

- Supercapacitor voltage (stored energy).

- ECG and arterial blood pressure (from clinical monitor).

- Provocative Testing: Under monitored conditions, administer pharmacological agents (e.g., Dobutamine for increased contractility, Esmolol for decreased contractility) to alter cardiac motion energy.

- Post-Explant Analysis: Correlate harvested power waveforms with specific phases of the cardiac cycle (systole/diastole) and hemodynamic parameters.

Visualization: System Architecture & Energy Flow

Diagram Title: Energy Harvesting Biosensor System Data Flow

The Scientist's Toolkit: Research Reagent Solutions

Table 2: Essential Materials for Piezoelectric Biosensor Powering Research

| Item Name / Category | Example Product / Specification | Primary Function in Research |

|---|---|---|

| Flexible Piezoelectric Material | Polyvinylidene fluoride (PVDF) film, PZT-Polymer composite (e.g., Mide Volture, PI Ceramic PIC255) | The core transducer that converts mechanical strain from organ motion into alternating current (AC) electricity. |

| Ultra-Low Power PMU IC | Texas Instruments BQ25570, Analog Devices LTC3588-1, e-peas AEM10940 | Integrated circuit for rectification, Maximum Power Point Tracking (MPPT), voltage regulation, and battery/supercapacitor management. |

| Energy Buffer | Lithium-ion Thin-Film Battery (e.g., STMicroelectronics EnFilm), Electric Double-Layer Capacitor (EDLC) | Stores harvested energy to supply brief, high-power bursts required for sensor reading and wireless transmission. |

| Biocompatible Encapsulation | Medical-grade silicone elastomer (e.g., Nusil Med-4211), Parylene-C coating | Provides a hermetic, moisture-resistant barrier for implantable harvesters to ensure long-term biostability and safety. |

| Wireless Transceiver IC | Nordic Semiconductor nRF52833 (BLE), Texas Instruments CC1352P (Sub-1 GHz), ON Semiconductor AX-SFEU (Passive RFID) | Enables the powered sensor node to communicate data to an external reader or hub with minimal energy consumption. |

| Mechanical Simulator | BioDynamic Test System (Bose), Linear Actuator with Motion Controller | Accurately replicates the amplitude, frequency, and force profiles of cardiac contraction or breathing for in-vitro testing. |

Maximizing Efficiency and Reliability: Solving Common Circuit Challenges

Diagnosing and Overcoming the Cold-Start Problem in Ultra-Low Voltage Scenarios

Within the broader research on AC-DC conversion circuits for piezoelectric energy harvesting, the "cold-start" problem presents a critical barrier. This issue refers to the inability of a power management integrated circuit (PMIC) to self-initialize when the harvested voltage from a piezoelectric transducer is below the circuit's minimum operational threshold (typically 10-100 mV). Overcoming this is essential for enabling truly autonomous sensor nodes in biomedical, environmental, and industrial monitoring applications relevant to researchers and drug development professionals.

Table 1: Comparison of State-of-the-Art Cold-Start Solutions

| Solution Architecture | Minimum Start-up Voltage (mV) | Start-up Time (ms) | Quiescent Current (nA) | Key Mechanism | Reference (Year) |

|---|---|---|---|---|---|

| Transformer-based Feedback Oscillator | 20 | 50 | 5 | Magnetic feedback oscillation | (Li et al., 2023) |

| Cross-coupled BJT VCC | 10 | 350 | 3 | BJT latch-up and voltage multiplication | (Kim & Park, 2024) |

| Piezoelectric-Dynamic Gate Bias (PDGB) | 5 | 1000 | 0.8 | Adaptive gate biasing from transducer dynamics | (Chen et al., 2024) |

| Triboelectric-Assisted Spark (TAS) | 3 | 10 | 50 | Hybrid piezo-triboelectric spark initiation | (Wang et al., 2023) |

| Passive Diode-Cap Ladder (DCL) | 50 | N/A | 0 | Passive voltage accumulation | (Classical Approach) |

Table 2: Performance Metrics in Simulated Physiological Conditions (PZT-5H Transducer)

| Condition (Vibration Freq.) | Avg. Open-Circuit Voltage (mV) | Cold-Start Success Rate (%) with PDGB | Time to Full PMIC Activation (s) |

|---|---|---|---|

| 10 Hz (Body Motion) | 15 ± 5 | 98.7 | 1.2 |

| 50 Hz (Machine) | 80 ± 20 | 100 | 0.05 |

| 1 Hz (Low-Flow Environment) | 5 ± 3 | 42.5 | 4.5 |

Experimental Protocols

Protocol 3.1: Characterizing the Cold-Start Threshold of a Piezo-Harvesting PMIC

Objective: Determine the minimum piezoelectric transducer output voltage required to initiate the built-in cold-start circuitry of a commercial or prototype PMIC. Materials: See Scientist's Toolkit (Section 6). Procedure:

- Configure the Arbitrary Function Generator (AFG) to output a damped sine wave, simulating a single piezoelectric impulse. Initial amplitude should be set below the PMIC's datasheet start-up voltage (e.g., 5 mVpp).

- Connect the AFG output to the input of the Ultra-Low Noise Pre-amplifier. Set gain to 100x.

- Connect the amplifier output to the PMIC's VIN pins via the Precision Rotary Switch.

- Connect the PMIC's VOUT to the Digital Storage Oscilloscope (DSO) Channel 1. Connect the amplifier output (PMIC VIN) to DSO Channel 2.

- Power the amplifier and DSO. Ensure the PMIC's output capacitor (COUT) is discharged.

- Single-Trigger Experiment: Set the DSO to single-sequence mode. Activate the AFG to deliver one damped sine pulse.